| Timing Terminology                                                                                                       |                                                                                                                                                                          |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Caution: terminology may vary slightly between vendors.                                                                  |                                                                                                                                                                          |  |  |  |  |

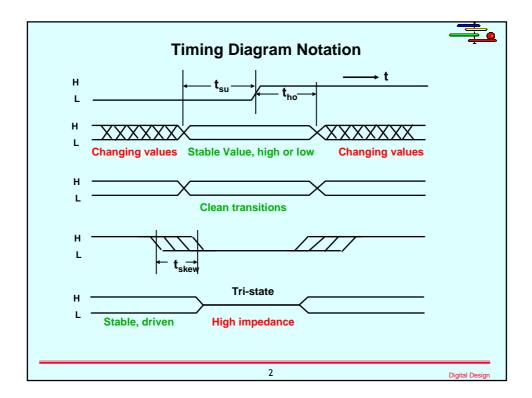

| Set-up time , t <sub>su</sub> :                                                                                          | the minimum length of time that a signal must be valid at a circuit input before a second triggering signal arrives at a second input.<br>Usually a clock                |  |  |  |  |

| Delay time , $t_{co}$ :                                                                                                  | the length of time that a circuit requires for its output(s) to begin to change in response to a triggering signal arriving at an input. (also called propagation delay) |  |  |  |  |

| <i>Hold time ,</i> t <sub>ho</sub> :                                                                                     | the minimum length of time that a signal must be kept valid<br>at a circuit input after a triggering signal has been received<br>at a second input.                      |  |  |  |  |

| <i>Timing skew</i> , t <sub>skew</sub> : the maximum range of times over which a particular signal transition can occur. |                                                                                                                                                                          |  |  |  |  |

|                                                                                                                          | Due to variations in driver output impedance                                                                                                                             |  |  |  |  |

|                                                                                                                          | Problems in clock distribution                                                                                                                                           |  |  |  |  |

|                                                                                                                          | 3 Digital Design                                                                                                                                                         |  |  |  |  |

| Symbo | I | Input                                     | Output                                                    |                |

|-------|---|-------------------------------------------|-----------------------------------------------------------|----------------|

|       | _ | The input<br>must be valid                | The output<br>will be valid                               |                |

|       |   | If the input<br>were to fall              | Then the output will fall                                 |                |

|       |   | If the input<br>were to rise              | Then the output<br>will rise                              |                |

| ××××  | x | Don't care,<br>it will work<br>regardless | Don't know, the<br>output value is<br>indeterminate       |                |

| >     | - | Nonsense                                  | High impedence,<br>tristate, HiZ,<br>Not driven, floating |                |

|       |   | 4                                         |                                                           | Digital Design |

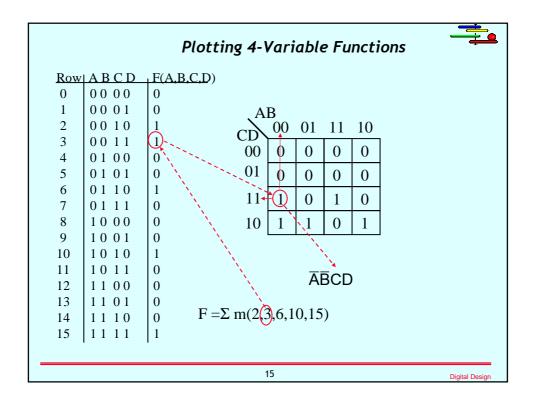

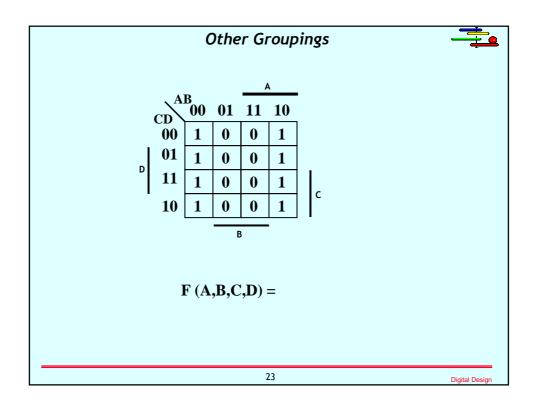

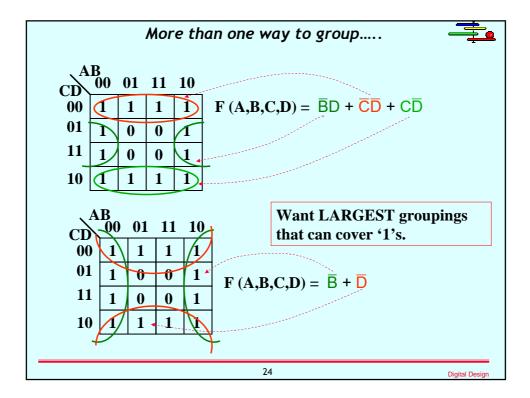

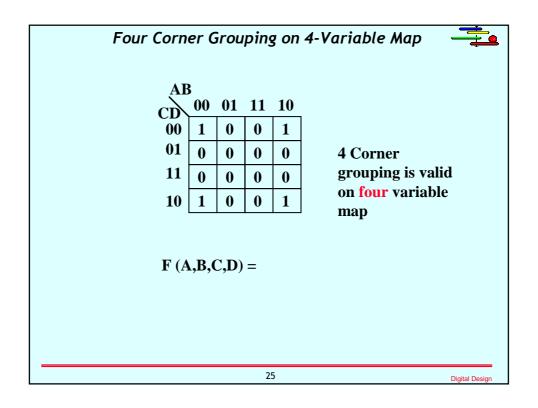

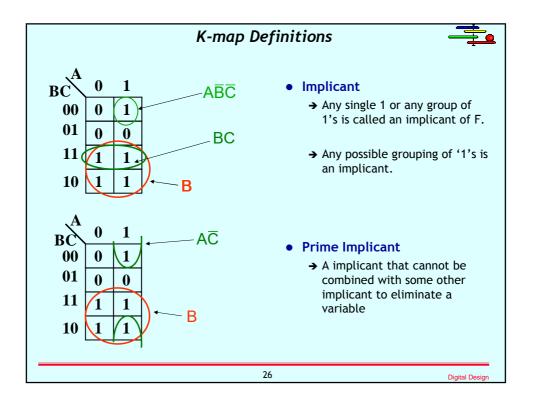

| Plo                                                   | otting 4-Variable Functions                            |

|-------------------------------------------------------|--------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | -                                                      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$  | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |